3Dチップパッケージングの威力

チップの高性能化、多機能化、低コスト化が進む中、ここ数年、3Dパッケージの開発が進んでいます。

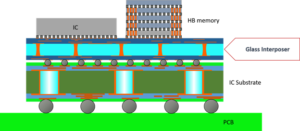

異なる機能を持つ異なるチップ(例えばメモリとICの組み合わせ)を積み重ね、接続することで、3Dパッケージング設計は距離を短縮し、より多くの相互接続を可能にします。その結果、より効率的で高速なシステムが実現します。

チップを重ねるには、分離層が必要です。この層は、チップ間の不要な電気的接続や漏れを防ぐアイソレーターとして機能します。また、チップの熱膨張に合わせた層の熱膨張が、放出される高熱によって生じる張力やひび割れを防ぎます。

この分離層にはシリコンが使われ、TSV(Through Silicon Via)と呼ばれる専用プロセスが導入されてきました。

しかし最近、シリコンの代替材料としてガラスが登場しました。その熱的・機械的特性は、3Dスタックにおいて他の材料と組み合わせた場合にいくつかの利点をもたらすからです。

図1 -ガラスインターポーザで絶縁チップを基板に接続した先進パッケージの概略図 – Vitrion社提供

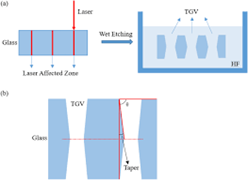

このようなViaまたはホールは、300um厚のガラスウェーハ上に直径30umの標準的なViaを使用する場合、基本的に1:10の高いフォームファクターを持っています。

TGV(Through Glass Via)とも呼ばれるこのようなビアを形成するために、最も一般的な方法は、レーザー支援化学エッチング法を使用することです。超高速レーザーとベッセルビーム(当社のGLASSモジュールで提供されるようなビーム整形)を併用することで、局所的なガラス改質/マイクロクラックを形成することができます。

この方法はうまくいきますが、作業者や環境に有害な化学薬品を使用する必要があります。

図2-ガラスモジュールとレーザー支援化学エッチングプロセスの原理

しかし、Amplitude社が開発した新しいレーザー機能(GHz)のおかげで、これはすぐに克服されるかもしれません。

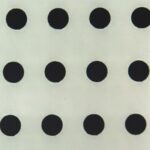

標準的な数十MHzの発振器をGHzレベルの内部繰り返し率バーストに置き換えると、光と物質の相互作用メカニズムが変わります。適切な量のパルスを使用すると、局所的な微小溶接効果を作り出すことができ、より速い速度で物質を除去することができます。

適切な焦点化条件と組み合わせると、高速で穴あけされた本当に高いアスペクト比を可能にする閉じ込められたアブレーションをもたらすことができます。

私たちのパートナーであるCELIAのような研究所で概念実証を行った後、産業界のプレーヤーは現在、このレーザーを産業界のブレークスルーにするために、レーザーのパラメーターをテストし、微調整しています。

数百ujのSatsuma Xと、新しく設計されたGHzフロントエンドを組み合わせることで、この新しい分野で選択されるツールとなり、今後数ヶ月のうちに採用される可能性があります。

図3-SatsumaXと初期のガラス掘削結果(CELIA提供)

ビデオ